ISSUED: V00 2011-06-07

# CONTENTS

| FUNCTIONS & FEATURES                        | - 3 |

|---------------------------------------------|-----|

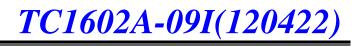

| BLOCK DIAGRAM                               | - 3 |

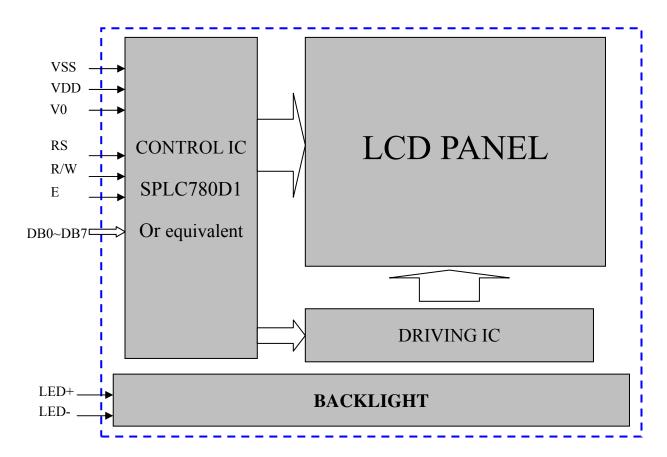

| MODULE OUTLINE DRAWING                      | - 4 |

| INTERFACE PIN FUNCTIONS                     | - 5 |

| ABSOLUTE MAXIMUM RATINGS (Ta = 25 °C)       | - 5 |

| DC ELECTRICAL CHARACTERISTICS               | - 5 |

| LED BACKLIGHT CHARACTERISTICS               | - 5 |

| CONNECTION WITH MCU                         | - 6 |

| Typical V0 connections for display contrast | - 6 |

| MPU Interface 4-Bit/8-Bit                   | - 6 |

| AC CHARACTERISTICS                          | - 7 |

| OPTICAL CHARACTERISTICS                     | - 9 |

| COMMAND TABLE                               | 10  |

| RESET FUNCTIONS                             | 12  |

| DISPLAY DATA RAM (DDRAM)                    | 14  |

| CHARACTER GENERATOR ROM                     | 15  |

| RELIABILITY TEST CONDITION                  | 16  |

| PRECAUTION FOR USING LCM MODULE             | 17  |

| OTHERS                                      | 18  |

| APPENDIX A: DATE CODE RULES                 | 18  |

| APPENDIX B: CHANGE NOTES                    | 18  |

## **FUNCTIONS & FEATURES**

- Construction

- Display Format

- Display Type

- Controller

- Interface

- Backlight

- Viewing Direction

- Driving Scheme

- Power Supply Voltage

- V<sub>LCD</sub> Adjustable For Best Contrast

- Operation temperature

- Storage temperature

- : COB(Chip-on-Board)

- : 16x2 Characters

- : STN, Transmissive, Negative, Blue

- : SPLC780D1 or equivalent controller

- : 4-bit\8-bit parallel interface

- : white\side lights

- : 6 O'clock

- : 1/16 Duty Cycle, 1/5 Bias

- : 5.0 V

- : 5.0 V (V<sub>OP</sub>.)

- : -10°C to +60°C

- : -20°C to +70°C

## **MODULE OUTLINE DRAWING**

## INTERFACE PIN FUNCTIONS

| Pin<br>No. | Symbol | Level      | Description                                                                |

|------------|--------|------------|----------------------------------------------------------------------------|

| 1          | VSS    | <b>0</b> V | Ground.                                                                    |

| 2          | VDD    | +5.0V      | Power supply for logic operating.                                          |

| 3          | V0     |            | Adjusting supply voltage for LCD driving.                                  |

|            |        |            | A signal for selecting registers:                                          |

| 4          | RS     | H/L        | 1: Data Register (for read and write)                                      |

|            |        |            | 0: Instruction Register (for write), Busy flag-Address Counter (for read). |

| 5          | R/W    | H/L        | R/W = "H": Read mode.                                                      |

| 3          | IX/ VV | 11/L       | R/W = "L": Write mode.                                                     |

| 6          | E      | H/L        | An enable signal for writing or reading data.                              |

| 7          | DB0    | H/L        |                                                                            |

| 8          | DB1    | H/L        |                                                                            |

| 9          | DB2    | H/L        |                                                                            |

| 10         | DB3    | H/L        | This is an 8-bit bi-directional data bus.                                  |

| 11         | DB4    | H/L        |                                                                            |

| 12         | DB5    | H/L        |                                                                            |

| 13         | DB6    | H/L        |                                                                            |

| 14         | DB7    | H/L        |                                                                            |

| 15         | LED+   | +5.0V      | Power supply for backlight.                                                |

| 16         | LED-   | <b>0</b> V | The backlight ground.                                                      |

# ABSOLUTE MAXIMUM RATINGS ( Ta = $25^{\circ}$ )

| Parameter                    | Symbol   | Min  | Max                  | Unit |

|------------------------------|----------|------|----------------------|------|

| Supply voltage for logic     | $V_{DD}$ | -0.3 | +7.0                 | V    |

| Supply voltage for LCD       | Vo       | 0    | V <sub>DD</sub> +0.3 | V    |

| Input voltage                | VI       | -0.3 | V <sub>DD</sub> +0.3 | V    |

| Normal Operating temperature | Тор      | -20  | +70                  | °C   |

| Normal Storage temperature   | Тѕт      | -30  | +80                  | °C   |

**Note:** Stresses beyond those given in the Absolute Maximum Rating table may cause operational errors or damage to the device. For normal operational conditions see AC/DC Electrical Characteristics.

# DC ELECTRICAL CHARACTERISTICS

| Parameter                 | Symbol | Condition | Min     | Тур | Max     | Unit |

|---------------------------|--------|-----------|---------|-----|---------|------|

| Supply voltage for logic  | VDD    |           | 4.8     | 5.0 | 5.2     | V    |

| Supply current for logic  | IDD    |           |         | 35  | 40      | mA   |

|                           |        | -10°C     |         |     |         |      |

| Operating voltage for LCD | VLCD   | 25℃       | 4.8     | 5.0 | 5.2     | V    |

|                           |        | +60°C     |         |     |         |      |

| Input voltage "H" level   | VIH    |           | 0.7 VDD |     | VDD+0.3 | V    |

| Input voltage "L" level   | VIL    |           | 0       |     | 0.2VDD  | V    |

# LED BACKLIGHT CHARACTERISTICS

| COLOR | Wavelength      | Operating              | Spectral line half          | Forward Current |

|-------|-----------------|------------------------|-----------------------------|-----------------|

| COLOK | $\lambda$ p(nm) | Voltage( $\pm 0.15$ V) | width $\Delta \lambda$ (nm) | (mA)            |

| white |                 | 3.2                    |                             | 30              |

**NOTE:** Do not connect +5V directly to the backlight terminals. This will ruin the backlight.

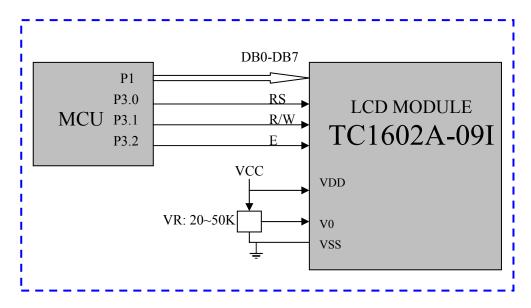

## **CONNECTION WITH MCU**

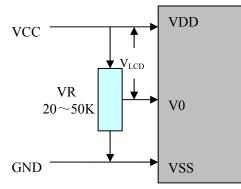

### (1) Typical V0 connections for display contrast

Adjust V0 to 0V (VLCD=+5 V) as an initial setting. When the module is operational, readjust V0 for optimal display appearance.

We recommend allowing field adjustment of V0 for all designs. The optimal value for V0 will change with temperature, variations in VDD, and viewing angle. V0 will also vary module-to-module and batch-to-batch due to normal manufacturing variations.

Ideally, adjustment to V0 should be available to the end user so each user can adjust the display to the optimal contrast for their required viewing conditions. As a minimum, your design should allow V0 to be adjusted as part of your product's final test.

Although a potentiometer is shown as a typical connection, V0 can be driven by your microcontroller, either by using a DAC or a filtered PWM. Displays that require V0 to be negative may need a level-shifting circuit. Please do not hesitate to contact Tinsharp application support for design assistance on your application.

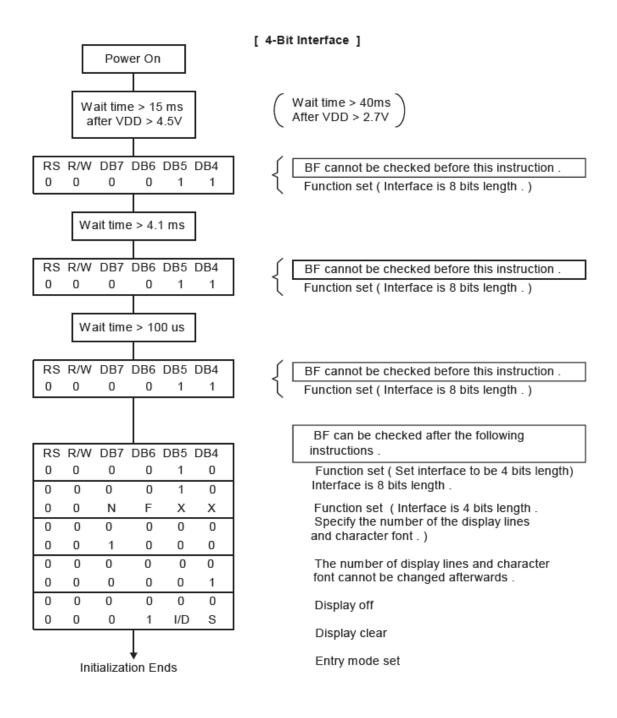

## (2) MPU Interface 4-bit/8-Bit

There are tow types of data operations: 4-bit and 8-bit operations. Using 4-bit MPU, the interfacing 4-bit data is transferred by 4-busline (DB4 $\sim$ DB7). Thus, DB0 to DB3 bus lines are not used. Using 4-bit MPU to interface 8-bit data requires tow times transferring. First, the higher 4-bit data is transferred by 4-busline (for 8-bit operation, DB7 $\sim$ DB4). Secondly, the lower 4-bit data is transferred by 4-busline (for 8-bit operation, DB7 $\sim$ DB4). For 8-bit data is transferred by 8-busline (DB0 $\sim$ DB7).

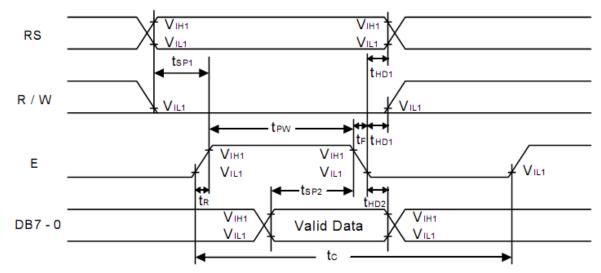

# **AC CHARACTERISTICS**

| Characteristics    | Cumhal                          |      | Limit | _    | 11.016 | Test Candition   |

|--------------------|---------------------------------|------|-------|------|--------|------------------|

| Characteristics    | Symbol                          | Min. | Тур.  | Max. | Unit   | Test Condition   |

| E Cycle Time       | to                              | 400  | -     | -    | ns     | Pin E            |

| E Pulse Width      | t <sub>PW</sub>                 | 150  | -     | -    | ns     | Pin E            |

| E Rise/Fall Time   | t <sub>R</sub> , t <sub>F</sub> | -    | -     | 25   | ns     | Pin E            |

| Address Setup Time | t <sub>SP1</sub>                | 30   | -     | - 0  | ns     | Pins: RS, R/W, E |

| Address Hold Time  | t <sub>HD1</sub>                | 10   | -     |      | ns     | Pins: RS, R/W, E |

| Data Setup Time    | t <sub>SP2</sub>                | 40   | -     |      | ns     | Pins: DB0 - DB7  |

| Data Hold Time     | t <sub>HD2</sub>                | 10   | -     |      | ns     | Pins: DB0 - DB7  |

### (1) Write Mode (Writing data from MPU to SPLC780D1)

### Write Mode Timing Diagram (Writing data from MPU to SPLC780D1)

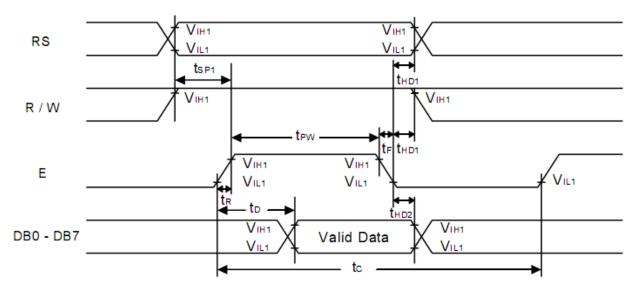

#### (2) Read Mode (Reading data from SPLC780D1 to MPU)

| Characteristics        | Symbol                          |      | Limit |      | - Unit | Test Condition   |

|------------------------|---------------------------------|------|-------|------|--------|------------------|

| Characteristics        | Symbol                          | Min. | Тур.  | Max. | - Unit | Test Condition   |

| E Cycle Time           | t <sub>c</sub>                  | 400  | -     | -    | ns     | Pin E            |

| E Pulse Width          | tw                              | 150  | -     |      | ns     | Pin E            |

| E Rise/Fall Time       | t <sub>R</sub> , t <sub>F</sub> | DV'  | -     | 25   | ns     | Pin E            |

| Address Setup Time     | t <sub>SP1</sub>                | 30   | -     |      | ns     | Pins: RS, R/W, E |

| Address Hold Time      | t <sub>HD1</sub>                | 10   | -     |      | ns     | Pins: RS, R/W, E |

| Data Output Delay Time | t₀                              | -    |       | 100  | ns     | Pins: DB0 - DB7  |

| Data hold time         | t <sub>HD2</sub>                | 5.0  |       | - 1  | ns     | Pin DB0 - DB7    |

#### Read Mode Timing Diagram (Reading data from SPLC780D1 to MCU)

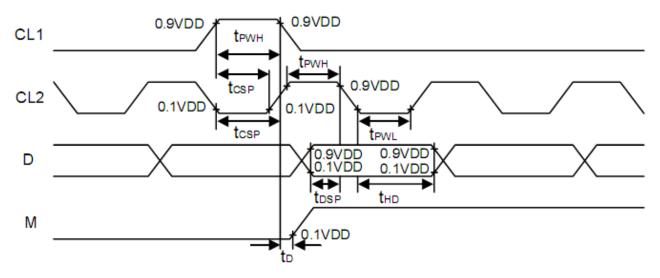

### (3) Interface mode with LCD driver (SPLC100B1)

| Characteristics        | Symbol           |       | Limit     |      | Unit | Test Condition |  |

|------------------------|------------------|-------|-----------|------|------|----------------|--|

| Characteristics        | Symbol           | Min.  | Min. Typ. |      | Unit | Test Condition |  |

| Clock pulse width high | t <sub>PWH</sub> | 800   | -         | -    | ns   | Pins: CL1, CL2 |  |

| Clock pulse width low  | tPWL             | 800   | -         | -    | ns   | Pins: CL1, CL2 |  |

| Clock setup time       | tcsp             | 500   | -         | -    | ns   | Pins: CL1, CL2 |  |

| Data setup time        | t <sub>DSP</sub> | 300   | -         | -    | ns   | Pins: D        |  |

| Data hold time         | t <sub>HD</sub>  | 300   | -         | -    | ns   | Pins: D        |  |

| M delay time           | t₀               | -1000 | -         | 1000 | ns   | Pins: M        |  |

#### Interface mode with SPLC100B1 Timing Diagram

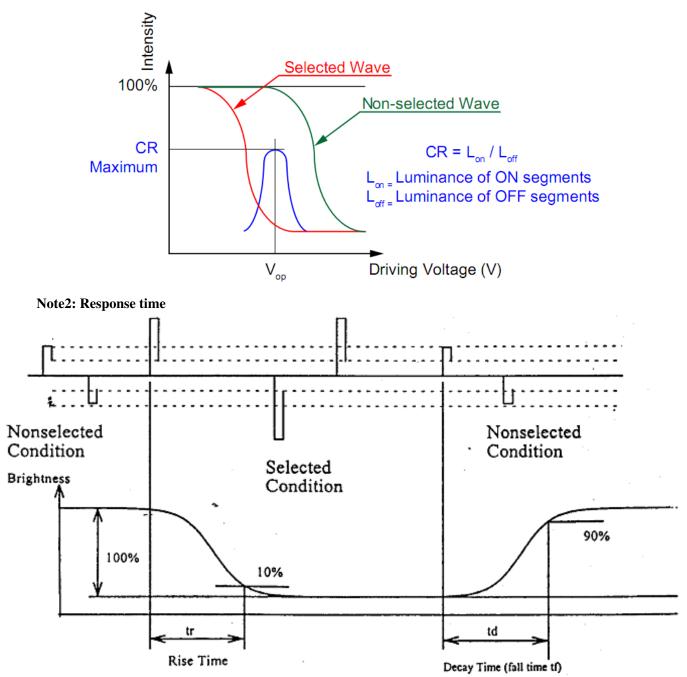

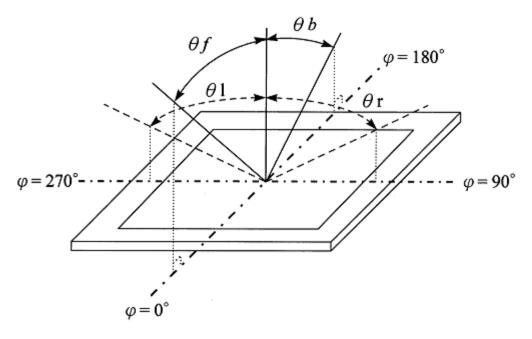

# **OPTICAL CHARACTERISTICS**

| ITEM                | SYMBOL | CONDITION  | MIN | TYP | MAX | UNIT | NOTE |

|---------------------|--------|------------|-----|-----|-----|------|------|

| Contrast ratio      | CR     | θ=0, Φ=0   | -   | 3   | -   |      |      |

| Response time(rise) | Tr     | 25℃        |     | -   | 250 | ma   |      |

| Response time(fall) | Td     | 23 C       |     | -   | 350 | ms   |      |

| Kesponse time(tan)  | θf     |            |     |     |     |      |      |

| Viewing angle       | θb     | <b>25℃</b> |     |     |     |      |      |

| Viewing angle       | θ1     | 230        |     | -   |     | dag  |      |

|                     | θr     |            |     | _   |     | deg. |      |

Note1: Definition Operation Voltage (Vop.)

#### Note3: Viewing angle

## **COMMAND TABLE**

|                            |                                       |   |                 | Ins             | tructi          | ion Co | ode |   |     |    |                                                                                                                                                 | Execution time<br>(Temp = 25℃) |        |              |

|----------------------------|---------------------------------------|---|-----------------|-----------------|-----------------|--------|-----|---|-----|----|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|--------------|

| Instruction                | RS RW DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 |   | Fosc=<br>190KHz | Fosc=<br>270KHz | Fosc=<br>350KHz |        |     |   |     |    |                                                                                                                                                 |                                |        |              |

| Clear Display              | 0                                     | 0 | 0               | 0               | 0               | 0      | 0   | 0 | 0   | 1  | Write "20H" to DDRAM<br>and set DDRAM address<br>to "00H" from AC                                                                               | 2.16ms                         | 1.52ms | 1.18ms       |

| Return Home                | 0                                     | 0 | 0               | 0               | 0               | 0      | 0   | 0 |     | 17 | Set DDRAM address to<br>"00H" from AC and<br>return cursor to its<br>original position if shifted.<br>The contents of DDRAM<br>are not changed. | 2.16ms                         | 1.52ms | 1.18ms       |

| Entry Mode<br>Set          | 0                                     | 0 | 0               | 0               | 0               | o      | 0   | Y | I/D | s  | Assign cursor moving<br>direction and enable the<br>shift of entire display                                                                     | 53µs                           | 38µs   | 29µ <b>s</b> |

| Display ON/<br>OFF Control | 0                                     | 0 | 0               | 0               | •               | 0      | 1   | D | с   | в  | Set display (D),<br>cursor(C), and blinking of<br>cursor(B) on/off control<br>bit.                                                              | 53µs                           | 38µs   | 29µs         |

| Cursor or<br>Display Shift               | 0 | 0 | 0  | 0   | 0   | 1   | S/C | R/L |     |     | Set cursor moving and<br>display shift control bit,<br>and the direction, without<br>changing of DDRAM<br>data.                                      | 53µs | 38µs | 29µs |

|------------------------------------------|---|---|----|-----|-----|-----|-----|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Function Set                             | 0 | 0 | 0  | 0   |     | DL  | N   | F   | -   | -   | Set interface data length<br>(DL: 8-bit/4-bit), numbers<br>of display line (N:<br>2-line/1-line) and, display<br>font type (F:5x10<br>dots/5x8 dots) | 53µs | 38µs | 29µs |

| Set CGRAM<br>Address                     | 0 | 0 | 0  | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in<br>address counter.                                                                                                             | 53µs | 38µs | 29µs |

| Set DDRAM<br>Address                     | 0 | 0 | 1  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in<br>address counter                                                                                                              | 53µs | 38µs | 29µs |

| Read Busy Flag<br>and Address<br>Counter | 0 | 1 | BF | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 | Whether during internal<br>operation or not can be<br>known by reading BF.<br>The contents of address<br>counter can also be<br>read.                |      |      |      |

| Write Data to<br>RAM                     | 1 | 0 | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM).                                                                                                          | 53µs | 38µs | 29µs |

| Read Data from<br>RAM                    | 1 | 1 | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM).                                                                                                           | 53µs | 38µs | 29µs |

Note1: "---": don't care

Note2: In the operation condition under -20°C ~ 75°C, the maximum execution time for majority of instruction sets is 100us, except two instructions, "Clear Display" and "Return Home", in which maximum execution time can take up to 4.1ms.

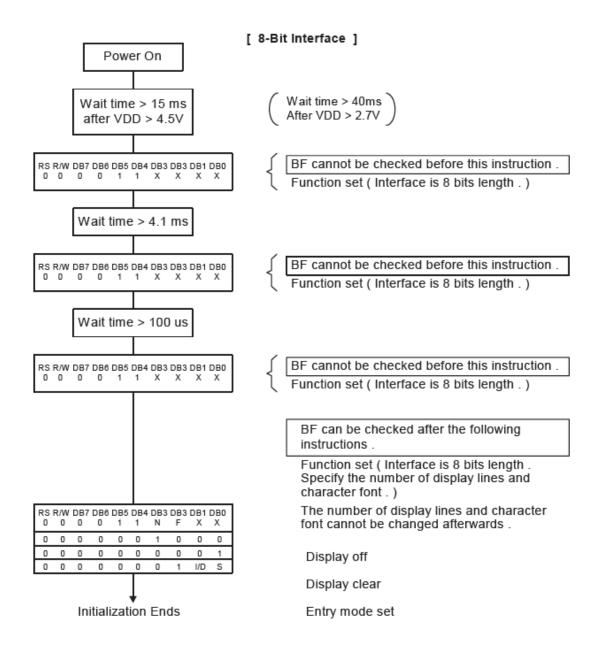

## **RESET FUNCTION**

At power on, SPLC780D1 starts the internal auto-reset circuit and executes the initial instructions. The initial procedures are shown as follows:

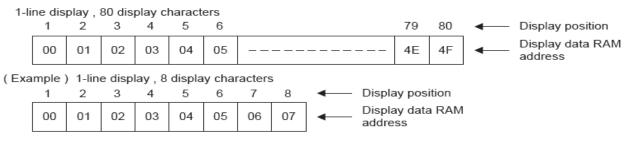

# DISPLAY DATA RAM (DD RAM)

The 80-bit DD RAM is normally used for storing display data. Those DD RAM not used for display data can be used as general data RAM. Its address is configured in the Address Counter.

When the display shift operation is performed , the display data RAM's address moves as :

| ( i | ) | Left shift |  |

|-----|---|------------|--|

|                      |          | Night Shin |       |       |    |    |

|----------------------|----------|------------|-------|-------|----|----|

| 01 02 03 04 05 06 00 | 06 07 08 | 4F 00      | 01 02 | 03 04 | 05 | 06 |

(ii) Diabt shift

#### **Timing Generation Circuit**

The timing generating circuit is able to generate timing signals to the internal circuits. In order to prevent the internal timing interface, the MPU access timing and the RAM access timing are generated independently.

#### LCD Driver Circuit

Total of 16 commons and 40 segments signal drivers are valid in the LCD driver circuit. When a program specifies the character fonts and line numbers, the corresponding common signals output drive-waveforms and the others still output unselected waveforms. The relationships between Display Data RAM Address and LCD' s position are depicted as follows.

#### **Character Generator ROM (CG ROM)**

Using 8-bit character code, the character generator ROM generates  $5 \times 8$  dots or  $5 \times 10$  dots character patterns. It also can generate 192's  $5 \times 8$  dots character patterns and 64's  $5 \times 10$  dots character patterns.

#### **Character Generator RAM (CG RAM)**

Users can easily change the character patterns in the character generator RAM through program. It can be written to  $5 \times 8$  dots, 8-character patterns or  $5 \times 10$  dots for 4-character patterns.

## **CHARACTER GENERATOR ROM**

## SPLC780D1-021A:

| Upper<br>4 bit<br>4 bit | шп | LLIH | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HLLH | HLHL | HLHH | HHLL | HHLH | HHHL | HERE |

|-------------------------|----|------|------|------|------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| LLLL                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LLLH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LLHL                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LLHH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LHLL                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LHLH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LHHL                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| LHHH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| HLLL                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| HLLH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| HLHL                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| HLHH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Œ    | *    |      |      |      |      |

| HHLL                    |    |      |      | Ľ    |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      | ×1   |      |      |      |      |

| HHLH                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

| HHHL                    |    |      |      | 2    |      |      |      |      | a second s |      |      |      |      |      | 1    |      |

| нннн                    |    |      |      |      |      |      |      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |      |      |      |

Ver.V00 2011-06-07

# **RELIABILITY TEST CONDITION**

| No. | TEST Item                                     | Content of Test                                                                                                                      | Test<br>Condition        | Applicable<br>Standard |

|-----|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|

| 1   | High temperature storage                      | Endurance test applying the high storage temperature for a long time.                                                                | 70° C 96hrs              |                        |

| 2   | Low temperature storage                       | Endurance test applying the low storage<br>Temperature for a long time                                                               | -20° C 96hrs             |                        |

| 3   | High temperature operation                    | Endurance test applying the electric stress<br>(Voltage & current)and the thermal stress to the<br>element for a long time           | 60° C 96hrs              |                        |

| 4   | Low temperature operation                     | Endurance test applying the electric stress<br>Under low temperature for a long time                                                 | -10° C 96hrs             |                        |

| 5   | High<br>temperature/<br>Humidity storage      | Endurance test applying the electric stress(Voltage & current) and Temperature/<br>Humidity stress to the element for a long time    | 40° C 90%RH<br>96hrs     |                        |

| 6   | High<br>temperature/<br>Humidity<br>operation | Endurance test applying the electric stress<br>(voltage & current)and temperature/<br>humidity stress to the element for a long time | 40° C 90%RH<br>96hrs     |                        |

| 7   | Temperature<br>cycle                          | Endurance test applying the low and high temperature<br>cycle.<br>-10° C →25° C→60° C<br>30min←5min←30min.(1 cycle)                  | -10° C/60° C<br>10 cycle |                        |

Supply voltage for logic system = 5V. Supply voltage for LCD system = Operating voltage at  $25^{\circ}$  C.

## **Mechanical Test**

| Vibration test            | Endurance test applying the vibration during transportation and using                  | 10~22Hz→1.5mmp-p<br>22~500Hz→1.5G<br>Total 0.5hour          |

|---------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Shock test                | Constructional and mechanical endurance test applying the shock during transportation. | 50G half sign wave 11<br>msede 3 times of each<br>direction |

| Atmospheric pressure test | Endurance test applying the atmospheric pressure during transportation by air          | 115mbar<br>40hrs                                            |

| Static electricity test   | Endurance test applying the electric stress to the terminal                            | VS=800V,RS-1.5K Ω<br>CS=100pF, 1 time                       |

### **Environmental condition**

The inspection should be performed at the 1metre height from the LCD module under 2 pieces of 40W white fluorescent lamps (Normal temperature  $20 \sim 25^{\circ}$ C and normal humidity  $60 \pm 15\%$ RH).

# PRECAUTION FOR USING LCM MODULE

- Please remove the protection foil of polarizer before using.

- The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- If the display panel is damaged and the liquid crystal substance inside it leaks out, do not get any in your mouth. If the substance come into contact with your skin or clothes promptly wash it off using soap and water.

- Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarize carefully.

- To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

Be sure to ground the body when handling the LCD module.

-Tools required for assembly, such as soldering irons, must be properly grounded.

-To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions. -The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

■ Storage precautions

When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

Keep the modules in bags designed to prevent static electricity charging under low temperature / normal humidity conditions (avoid high temperature / high humidity and low temperatures below  $0^{\circ}$ C). Whenever possible, the LCD modules should be stored in the same conditions in which they were shipped from our company.

# OTHERS

- Liquid crystals solidify at low temperature (below the storage temperature range) leading to defective orientation of liquid crystal or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subjected to a strong shock at a low temperature.

- If the LCD modules have been operating for a long time showing the same display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. Abnormal operating status can be resumed to be normal condition by suspending use for some time. It should be noted that this phenomena does not adversely affect performance reliability.

- To minimize the performance degradation of the LCD modules resulting from caused by static electricity, etc. exercise care to avoid holding the following sections when handling the modules :

- Exposed area of the printed circuit board

- Terminal electrode sections

## A. DATE CODE RULES

#### A.1. DATE CODE FOR SAMPLE

### A.2. DATE CODE FOR PRODUCTION

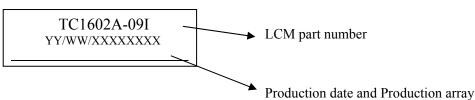

A. TC1602A-09I represents LCM part number

C. YY/WW represents Year, Week

YY—Year WW—Week

XXXXXXXX—Production array No.

## **B. Change Notes:**

| Ver. | Descriptions | Editor | Date       |

|------|--------------|--------|------------|

| V00  | First Issue  | ZXQ    | 2011-06-07 |

|      |              |        |            |

|      |              |        |            |

|      |              |        |            |